電子元♍国产熟女视频🌈器(qi)件電路布(bu)局的可靠(kao)性設計--跳(tiao)線

9.

6.1 電(dian)子線路的(de)可靠性設(she)計原則

采(cai)用各種電(dian)子元器件(jian)進行系統(tong)或整機線(xian)路設計時(shi),設計師不(bu)僅必須考(kao)慮如何實(shi)現規定的(de)功能,而且(qie)應該考慮(lü)采用何種(zhong)設計方案(an)才能充分(fen)發揮元器(qi)件固有可(ke)靠性的潛(qian)力,提高系(xi)統或整機(ji)的可靠性(xing)水平。這就(jiu)是通常所(suo)說的可靠(kao)性設計。

電(dian)子線路的(de)可靠性設(she)計是一個(ge)内容相當(dang)廣泛而具(ju)體的問題(ti)💋,采用不同(tong)類型的器(qi)件或者要(yao)實現不同(tong)的電路功(gong)能😍,都會有(you)不同的可(ke)靠性設計(ji)考慮。這裏(li)首先給出(chu)電子線路(lu)🌈可靠性設(she)計的一些(xie)基本原則(ze),在8.6.2節再給(gei)出幾種具(ju)體電路的(de)設計規🏒則(ze)。

1. 簡化設計(ji)

由于可靠(kao)性是電路(lu)複雜性的(de)函數,降低(di)電路的複(fu)雜性可以(yi)相⛹🏻♀️應的提(ti)高電路的(de)可靠性,所(suo)以,在實現(xian)⭐規定🌈功能(neng)的前提下(xia),應盡量使(shi)電路結構(gou)簡單,最大(da)💘限度的減(jian)少所用元(yuan)器件的類(lei)型和品🔞種(zhong),提高元器(qi)件的複用(yong)率。這是提(ti)❄️高電路可(ke)靠性的一(yi)🏃🏻♂️種簡單而(er)🧑🏾🤝🧑🏼實用的方(fang)法💋。

簡化設(she)計的具體(ti)方案可以(yi)根據實際(ji)情況來定(ding),一般😍使用(yong)的方法有(you):

(1)多個通道(dao)共用一個(ge)電路或器(qi)件。

(2)在保證(zheng)實現規定(ding)功能指标(biao)的前提下(xia),多采用集(ji)成電路,少(shao)采用分立(li)器件,多采(cai)用規模較(jiao)大的集成(cheng)電路,少采(cai)用規模👣較(jiao)小🏒的集成(cheng)電路。集成(cheng)度的提高(gao)可以減少(shao)元器件之(zhi)間的連線(xian)、接🏃🏻點以及(ji)🔞封裝的數(shu)目,而這些(xie)連接點的(de)可🥰靠性常(chang)常是造成(cheng)電路失效(xiao)的主要原(yuan)因。

(3)在邏輯(ji)電路的設(she)計中,簡化(hua)設計的重(zhong)點應該放(fang)在減✌️少邏(luo)輯器♍件的(de)數目,其次(ci)才是減少(shao)門或輸入(ru)端的數目(mu)。因爲一般(ban)而言,與減(jian)少電路的(de)複雜度相(xiang)比較,提高(gao)電路的集(ji)成度對于(yu)提高系統(tong)可靠性的(de)效果更爲(wei)明顯。

(4)多采(cai)用标準化(hua)、系列化的(de)元器件,少(shao)采用特殊(shu)的或未經(jing)定型和考(kao)驗的元器(qi)件。

(5)能用軟(ruan)件完成的(de)功能,不要(yao)用硬件實(shi)現。

(6)能用數(shu)字電路實(shi)現的功能(neng),不要用模(mo)拟電路完(wan)成,因爲數(shu)字電路的(de)可靠性和(he)标準化程(cheng)度相對較(jiao)高。但是,有(you)時模拟電(dian)路的功能(neng)用數字電(dian)路實現會(hui)導緻器件(jian)數目的明(ming)顯增加,這(zhe)時就要根(gen)據具體情(qing)況統籌考(kao)慮,力求選(xuan)用最佳方(fang)案。

在簡化(hua)設計時應(ying)注意三點(dian)::一是減少(shao)元器件不(bu)會✉️導🍓緻😘其(qi)它元🧑🏽🤝🧑🏻器件(jian)承受應力(li)的增加,或(huo)者對其它(ta)元😍器件的(de)性能要求(qiu)更加苛刻(ke);二是在用(yong)一種元器(qi)件完成多(duo)種功能時(shi),要确認該(gai)種器件在(zai)性能指标(biao)和可靠性(xing)方面是否(fou)能夠同時(shi)滿足幾個(ge)方面的要(yao)求🐇;三是爲(wei)滿足系統(tong)安全性、穩(wen)定性、可測(ce)❌性、可維修(xiu)性🔆或降額(e)和冗餘⛹🏻♀️設(she)計等的要(yao)求所增加(jia)的電路或(huo)元📐器件不(bu)能省略。

2. 低(di)功耗設計(ji)

電子系統(tong)向着小型(xing)化和高密(mi)度化發展(zhan),使得其内(nei)部🎯熱功率(lü)㊙️密度增加(jia),可靠性随(sui)之降低。降(jiang)低電路的(de)功耗🐪,是減(jian)少系統内(nei)🆚部溫升的(de)主要途徑(jing)。這可以從(cong)兩方面🌈着(zhe)手,一是盡(jin)量采用低(di)功耗器件(jian),如在滿足(zu)工作速度(du)的情況下(xia),盡量采用(yong)CMOS電路。而不(bu)用TTL電路;二(er)是在完成(cheng)規🧡定功能(neng)的前提下(xia),盡量簡化(hua)邏輯電路(lu),并更多的(de)讓軟件來(lai)完成硬件(jian)的功能,以(yi)減少整機(ji)🍓硬件的數(shu)量。

3. 保護電(dian)路設計

電(dian)子系統在(zai)工作中可(ke)能會受到(dao)各種不适(shi)當應力🔞或(huo)外界幹擾(rao)信号的影(ying)響,造成電(dian)路工作不(bu)正常,嚴重(zhong)時會導緻(zhi)内部器件(jian)的損壞。爲(wei)此,在電路(lu)設計中,有(you)必要🔅根據(ju)具體情況(kuang)設計必要(yao)的保護電(dian)路。如在電(dian)路的信号(hao)輸入端設(she)計靜電保(bao)護電路,在(zai)電源輸入(ru)端設計浪(lang)湧幹擾抑(yi)制電路,在(zai)高頻高速(su)電路中🧑🏽🤝🧑🏻加(jia)入噪聲抑(yi)制或吸收(shou)網絡。具⚽體(ti)保護電路(lu)的形式可(ke)參閱本書(shu)有關章節(jie)。

4. 靈敏度分(fen)析

組成電(dian)子系統的(de)各個電路(lu)對于系統(tong)可靠性的(de)貢獻并♌不(bu)相⭐同,而組(zu)成電路的(de)各個元器(qi)件對于該(gai)電路可靠(kao)性的貢獻(xian)也不會一(yi)樣。常常會(hui)有這樣的(de)情況,某個(ge)元器件的(de)參數退化(hua)嚴重,但對(dui)💃電路性能(neng)的影響甚(shen)微;而另一(yi)個元器件(jian)稍有變化(hua),就對電路(lu)性💯能産生(sheng)顯著影響(xiang)。這是因🧡爲(wei)一個元器(qi)件對于電(dian)路可靠性(xing)的影響(或(huo)一個子電(dian)路對于系(xi)統可靠性(xing)的影響)不(bu)僅🌐取決于(yu)該元器件(jian)(或子電路(lu))自身的質(zhi)量,而且取(qu)決于該元(yuan)器件(或子(zi)電路)造成(cheng)電路(或系(xi)統)性能變(bian)化的靈敏(min)度。因此,在(zai)電🐕路設計(ji)中,應進行(hang)靈敏度分(fen)析,确定對(dui)電路性能(neng)影響顯著(zhe)的關鍵元(yuan)器💋件或子(zi)電路。對其(qi)進行重點(dian)設計。靈敏(min)度分析可(ke)借助于現(xian)有的電路(lu)模拟器或(huo)邏輯模拟(ni)器完成。這(zhe)是🌂提高電(dian)路可靠性(xing)的一個經(jing)濟有效的(de)方⭐法。

5. 基于(yu)元器件的(de)穩定參數(shu)和典型特(te)性進行設(she)計

電路設(she)計通常必(bi)須依據所(suo)選用器件(jian)的參數指(zhi)标來進行(hang)。爲🥰了❓保證(zheng)電路的可(ke)靠性,隻要(yao)可能,電路(lu)性能應該(gai)基于器件(jian)的最穩🤟定(ding)的參數來(lai)設計,同時(shi)應留出一(yi)些允許變(bian)化的餘量(liang)。對于那些(xie)由于工藝(yi)離🌂散性以(yi)及随時間(jian)、溫度和其(qi)它環境應(ying)力而變化(hua)的不太穩(wen)定的性能(neng)參數,設計(ji)時應給予(yu)更爲寬容(rong)的💚限制。對(dui)于那些不(bu)确定的無(wu)法控制的(de)性能參數(shu),設計時不(bu)宜采納,否(fou)則無法保(bao)證電路的(de)可靠性和(he)制造♈的可(ke)重複性。如(ru)果産品手(shou)冊中 記載(zai)☀️有所需的(de)特性曲線(xian)圖、外部電(dian)路參數或(huo)典型應用(yong)電路時,應(ying)盡可能使(shi)用該特性(xing)曲線或電(dian)路方案進(jin)行設計。

6. 均(jun)衡設計

在(zai)設計一個(ge)電子系統(tong)時,總是要(yao)先将其分(fen)割爲若幹(gan)個電路塊(kuai),以便完成(cheng)不同的功(gong)能。在系統(tong)分割時,應(ying)注意電路(lu)功能和結(jie)構的均衡(heng)性,這樣對(dui)提高系統(tong)可靠性有(you)利。這主要(yao)體現在兩(liang)個方面:一(yi)是每塊電(dian)路的功能(neng)應相對完(wan)整,盡量減(jian)少各個💃電(dian)路之間的(de)聯接,以削(xue)弱互連對(dui)電路可靠(kao)性的影響(xiang);二是各個(ge)電流所含(han)元器件的(de)數量不要(yao)過于集中(zhong)帶來的不(bu)可靠因素(su),同時也方(fang)便了裝配(pei)工藝設計(ji)。

7. 三次設計(ji)

三次設計(ji)包括系統(tong)設計、參數(shu)設計和容(rong)差設計。系(xi)統設計是(shi)📧指一般意(yi)義上的設(she)計;參數設(she)計是利用(yong)正交設計(ji)💜法結合計(ji)算機輔助(zhu)設計,找到(dao)穩定性好(hao)的合理參(can)數組🈚,是三(san)次設計的(de)核心;容差(cha)設計則是(shi)在系統的(de)最佳參數(shu)💜組合确定(ding)之後,合理(li)規劃組成(cheng)💚系統的各(ge)個🌍元器件(jian)的容差,使(shi)産品物美(mei)價廉。采用(yong)三次設計(ji)方法獲得(de)的産品具(ju)有高的信(xin)噪比,對于(yu)元器件的(de)公差與老(lao)化、工作和(he)環境條件(jian)的波動變(bian)化等具有(you)很強的忍(ren)受能力,保(bao)證長時間(jian)🚶正常工作(zuo)🌈。因此,在所(suo)🤞采用的元(yuan)器件質量(liang)😄等級相同(tong)的條件下(xia),通過三次(ci)設計的電(dian)路的可靠(kao)性明顯高(gao)🚩于未作三(san)次設計的(de)電路。

8. 冗餘(yu)設計和降(jiang)額設計

冗(rong)餘設計也(ye)稱餘度設(she)計,它是在(zai)系統或設(she)備中的關(guan)鍵電路部(bu)位,設計一(yi)種以上的(de)功能通道(dao),當一個功(gong)能通道發(fa)生故障時(shi),可✔️用另一(yi)個通道代(dai)替,從而可(ke)使局部故(gu)障不影響(xiang)整個系💘統(tong)或設備的(de)正常工作(zuo)。采用冗餘(yu)設計,使得(de)用相對低(di)可靠的元(yuan)器件構成(cheng)可靠的系(xi)統或設備(bei)成👣爲可能(neng)。但是,采用(yong)冗餘設👈計(ji)會使電路(lu)🥵的複雜性(xing)以及系統(tong)的體積、重(zhong)量♌、功耗和(he)成本增加(jia),一般隻用(yong)于那些安(an)全性要求(qiu)非常高而(er)✊且難以維(wei)修的系統(tong)。

9. 可靠性預(yu)計

爲了驗(yan)證可靠性(xing)設計的效(xiao)果,根據系(xi)統可靠性(xing)的要求,電(dian)路設計完(wan)成後,可對(dui)關鍵電路(lu)的失效率(lü)進行預計(ji),預計所依(yi)據的模型(xing)和方法見(jian)國軍标GJB299《電(dian)子💯設備可(ke)靠性預計(ji)手冊》。

9.6.2 常用(yong)集成電路(lu)的應用設(she)計規則

在(zai)電路設計(ji)時,除了以(yi)上所述的(de)通用設計(ji)原則之外(wai),還要根據(ju)所用器件(jian)的具體情(qing)況,采用不(bu)同的設計(ji)規則。下👌面(mian)給出用📐幾(ji)種常用集(ji)成電路進(jin)行電路設(she)計時應該(gai)遵循的一(yi)些規則。這(zhe)些規則所(suo)依據的設(she)計原理大(da)多已經在(zai)本書的有(you)關章節裏(li)予以闡述(shu),這裏不再(zai)贅述。

1. TTL電路(lu)應用設計(ji)規則

(1) 電源(yuan)

•穩定性應(ying)保持在±5%之(zhi)内;

•紋波系(xi)數應小于(yu)5%;

•電源初級(ji)應有射頻(pin)旁路。

(2)去耦(ou)

•每使用8塊(kuai)TTL電路就應(ying)當用一個(ge)0.01~0.1μF的射頻電(dian)容器對電(dian)🌈源電壓進(jin)行去耦。去(qu)耦電容的(de)位置應僅(jin)可能地靠(kao)近集成電(dian)路,二者之(zhi)間的距離(li)應在15cm之内(nei)。每塊印制(zhi)✔️電路闆也(ye)應用一隻(zhi)容量更大(da)些的低電(dian)感電容器(qi)😘對電源進(jin)行去耦。電(dian)容器類型(xing)的選擇方(fang)🐇法參見8.1.1節(jie)。

(3)輸入信号(hao)

•輸入信号(hao)的脈沖寬(kuan)度應長于(yu)傳播延遲(chi)時間,以免(mian)🔞出現反射(she)噪⭐聲;

•要求(qiu)邏輯“0”輸出(chu)的器件,其(qi)不使用的(de)輸入端應(ying)将其接☎️地(di)或與同一(yi)門電路的(de)在用輸入(ru)端相連;

•要(yao)求邏輯“1”輸(shu)出的器件(jian),其不使用(yong)的輸入端(duan)應連接到(dao)🌐一📱個大于(yu)2.7V的電壓上(shang)。爲了不增(zeng)加傳輸延(yan)遲時間和(he)噪聲敏🏃♀️感(gan)度🔞,所接電(dian)壓不要超(chao)過該電路(lu)的電壓最(zui)大額🆚定值(zhi)5.5V;

•不使用的(de)器件,其所(suo)有的輸入(ru)端都應按(an)照使功耗(hao)最低🆚的方(fang)☂️法連接,具(ju)體的處理(li)方法可參(can)閱8.1.6節;

•在使(shi)用低功耗(hao)肖特基TTL電(dian)路時,應保(bao)證其輸入(ru)端不出現(xian)🔆負電📐壓,以(yi)免電流流(liu)入輸入箝(qian)位二極管(guan);

•時鍾脈沖(chong)的上升時(shi)間和下降(jiang)時間應盡(jin)可能的短(duan),以便提☔高(gao)電🏒路的抗(kang)幹擾能力(li);

•通常時鍾(zhong)脈沖處于(yu)高态時,觸(chu)發器的數(shu)據不應改(gai)變。若一例(li)外,應查閱(yue)有關的數(shu)據規範;

•擴(kuo)展器應盡(jin)可能地靠(kao)近被擴展(zhan)的門,擴展(zhan)器的節點(dian)上👈不能有(you)容性負載(zai);

•在長信号(hao)線的接收(shou)端應接一(yi)個500Ω~1kΩ的上拉(la)電阻,以便(bian)✉️增🏃加💯噪聲(sheng)🐕容❓限和縮(suo)短上升時(shi)間。

(4)輸出信(xin)号

•集電極(ji)開路器件(jian)的輸出負(fu)載應連接(jie)到小于等(deng)于最大額(e)定值的電(dian)壓上,所有(you)其它器件(jian)的輸出負(fu)載🧡應連接(jie)到VCC上;

•長信(xin)号線應該(gai)由專門爲(wei)其設計的(de)電路驅動(dong),如線驅動(dong)器、緩沖器(qi)等;

•從線驅(qu)動器到接(jie)收電路的(de)信号回路(lu)線應是連(lian)續的,應采(cai)用♉特性阻(zu)抗約爲100Ω的(de)同軸線或(huo)雙扭線;

•在(zai)長信号線(xian)的驅動端(duan)應加一隻(zhi)小于51Ω的串(chuan)聯電阻,以(yi)便消除🌈可(ke)能出現的(de)負過沖。

(5)并(bing)聯應用

•除(chu)三态輸出(chu)門外,有源(yuan)上拉門不(bu)得并聯連(lian)接。隻有一(yi)種情況例(li)外,即并聯(lian)門的所有(you)輸入端和(he)輸出端均(jun)并聯在一(yi)起,而且♍這(zhe)些門電路(lu)封裝在同(tong)一外殼✌️内(nei);

•某些TTL電路(lu)具有集電(dian)極開路輸(shu)出端,允許(xu)将幾個電(dian)路的開集(ji)電極輸出(chu)端連接在(zai)一起,以實(shi)現“線與”功(gong)能。但應在(zai)該輸出端(duan)加一個上(shang)拉電阻,以(yi)便提供足(zu)夠的驅動(dong)信号和提(ti)高☎️抗幹擾(rao)能力,上🤩拉(la)電阻的阻(zu)值應根據(ju)該電路的(de)🔆扇出能力(li)來确定。

2. CMOS電(dian)路應用設(she)計規則

(1)電(dian)源

•穩定性(xing)應保持在(zai)±5%之内;

•紋波(bo)系數應小(xiao)于5%;

•電源初(chu)級應有射(she)頻旁路;

•如(ru)果CMOS電路自(zi)身和其輸(shu)入信号源(yuan)使用不同(tong)的電源,則(ze)開🔴機時應(ying)首先接通(tong)CMOS電源,然後(hou)接通信号(hao)源,關機🤟時(shi)應該首先(xian)關⛱️閉信号(hao)源🈲,然後關(guan)閉CMOS電源。

(2)去(qu)耦

•每使用(yong)10~15塊CMOS電路就(jiu)應當用一(yi)個0.01~0.1μF的射頻(pin)電容器對(dui)電源㊙️電壓(ya)進🏃行去耦(ou)。去耦電容(rong)的位置應(ying)僅可能地(di)靠👄近集成(cheng)電路,二者(zhe)之間的距(ju)離應在15之(zhi)内。每塊印(yin)制💋電路闆(pan)也應用一(yi)隻容💯量更(geng)大些的低(di)電感電容(rong)器對電源(yuan)進行去耦(ou)。

(3)輸入信号(hao)

•輸入信号(hao)電壓的幅(fu)度應限制(zhi)在CMOS電路電(dian)源電壓範(fan)🙇♀️圍之内,以(yi)免引發闩(shuan)鎖;

•多餘的(de)輸入端在(zai)任何情況(kuang)下都不得(de)懸空,應适(shi)當的連🏃♀️接(jie)到CMOS電路的(de)電壓正端(duan)或負端上(shang);

•當CMOS電路由(you)TTL電路驅動(dong)時,應該在(zai)CMOS電路的輸(shu)入端與VCC之(zhi)間連一個(ge)上拉電阻(zu);

•在非穩态(tai)和單穩态(tai)多諧振蕩(dang)器等應用(yong)中,允許CMOS電(dian)🌍路有一定(ding)的🧑🏾🤝🧑🏼輸入電(dian)流(通過保(bao)護二極管(guan)),但應在其(qi)輸入加接(jie)一隻🥵串聯(lian)💁電阻,将輸(shu)入電流限(xian)制在微安(an)級的水平(ping)上。

(4) 輸出信(xin)号

•輸出電(dian)壓的幅度(du)應限制在(zai)CMOS電路電源(yuan)電壓範圍(wei)之内,以免(mian)❓引發闩鎖(suo);

•長信号線(xian)應該由專(zhuan)門爲其設(she)計的電路(lu)驅動,如線(xian)驅動器、緩(huan)沖器等;

•應(ying)避免在CMOS電(dian)流的輸出(chu)端接大于(yu)500pF的電容負(fu)載;

•CMOS電路的(de)扇出應根(gen)據其輸出(chu)容性負載(zai)量來确定(ding),通常可按(an)下式計算(suan):

( 9.6 )

式中,FO爲扇(shan)出,CL爲CMOS電路(lu)的額定容(rong)性負載電(dian)容,0.8是容性(xing)👌負載🌈的🤞降(jiang)額☎️系數,CI爲(wei)CMOS電路的額(e)定輸入電(dian)容。

(5)并聯應(ying)用

•除三态(tai)輸出門外(wai),有源上拉(la)門不得并(bing)聯連接。隻(zhi)有一種情(qing)況例外,即(ji)并聯門的(de)所有輸入(ru)端均并聯(lian)在一起,而(er)且這些門(men)電路封裝(zhuang)在同一外(wai)殼内。

3.線性(xing)放大器應(ying)用設計規(gui)則

(1) 電源

•穩(wen)定性應保(bao)持在±1%之内(nei);

•紋波系數(shu)應小于1%;

•電(dian)源初級應(ying)有射頻旁(pang)路;

(2) 去耦

•每(mei)使用10塊線(xian)性集成電(dian)路就應當(dang)用一個0.01~0.1μF的(de)射頻電🐪容(rong)器對電源(yuan)電壓進行(hang)去耦。去耦(ou)電容的位(wei)置應僅🤞可(ke)能地靠近(jin)集成電😄路(lu),二者之間(jian)的距離應(ying)在15cm之内。每(mei)塊印制電(dian)路🏃🏻闆也應(ying)用一隻💋容(rong)量更大些(xie)的低電感(gan)電容器對(dui)電源進行(hang)去耦。

(3) 輸入(ru)信号

•差模(mo)輸入電壓(ya)和共模輸(shu)入電壓均(jun)不應超過(guo)它們的最(zui)大額定💚值(zhi)的60%;

•所有不(bu)使用的輸(shu)入端均應(ying)按照使功(gong)耗最低的(de)方式進行(hang)🎯連接;

•如果(guo)器件具有(you)兩個以上(shang)的外部調(diao)整點,必須(xu)多次調整(zheng),僅一次是(shi)不行的。

(4) 輸(shu)出信号

•長(zhang)信号線應(ying)該由專門(men)爲其設計(ji)的電路驅(qu)動,如線驅(qu)動器🥰、緩沖(chong)🔞器等;

•從線(xian)驅動器到(dao)接收電路(lu)的信号回(hui)路線應采(cai)用連續🔴同(tong)軸線或🌐雙(shuang)扭線,其特(te)性阻抗應(ying)與連接端(duan)口的阻抗(kang)相匹🙇♀️配。

4. 線(xian)性電壓調(diao)整器應用(yong)設計規則(ze)

(1)輸入電壓(ya)

•輸入電壓(ya)不應超過(guo)其最大額(e)定值的80%;

•差(cha)分輸入電(dian)壓應該比(bi)推薦的最(zui)小電壓大(da)20%,以保持适(shi)✌️當的輸出(chu)電壓。

(2)輸出(chu)負載

•最大(da)輸出負載(zai)不得超過(guo)其最大額(e)定值的80%;

•如(ru)果器件内(nei)部沒有包(bao)含短路保(bao)護電路,則(ze)應設計外(wai)部短路保(bao)護電路。

(3)散(san)熱

•電壓調(diao)整器應該(gai)安裝散熱(re)器,其散熱(re)面積應能(neng)夠散掉👅器(qi)件承💚受最(zui)大功率時(shi)所産生的(de)熱量。

9.6.3 印制(zhi)電路闆布(bu)線設計

目(mu)前電子元(yuan)器件用于(yu)各類電子(zi)設備和系(xi)統時,仍然(ran)以印制電(dian)路闆爲主(zhu)要裝配方(fang)式。實踐證(zheng)明,即使電(dian)原理圖💛設(she)計正确,印(yin)制電路闆(pan)布線設計(ji)不當,也會(hui)對器件的(de)可靠性産(chan)生不利的(de)影響。例如(ru),将印制👌電(dian)路闆用于(yu)裝配高速(su)數字集成(cheng)電路時,電(dian)路上出現(xian)的瞬變電(dian)流通過印(yin)制🐇導線時(shi),會産生沖(chong)擊電流🙇🏻。如(ru)果印制導(dao)線的阻抗(kang)比較大,特(te)别是電感(gan)較大時,這(zhe)種沖擊電(dian)流的幅值(zhi)會🧡很大,有(you)可能對器(qi)件造成損(sun)害。如果印(yin)制闆兩條(tiao)細平行線(xian)靠得很近(jin),則會形成(cheng)信号波形(xing)的延遲,在(zai)傳輸線的(de)終端形成(cheng)反射噪聲(sheng)。因此,在設(she)計印制闆(pan)布線的時(shi)候,應注意(yi)采用正确(que)的方法。

1. 電(dian)磁兼容性(xing)設計

電磁(ci)兼容性(EMC)是(shi)指電子系(xi)統及其元(yuan)部件在各(ge)種電磁♋環(huan)😘境中⭕仍能(neng)夠協調、有(you)效地進行(hang)工作的能(neng)力。EMC設計的(de)目的是既(ji)能抑制各(ge)種外來的(de)幹擾,使電(dian)路和設備(bei)在規定的(de)電磁環境(jing)中能正常(chang)工💘作,同時(shi)又能減少(shao)其本身對(dui)其它設備(bei)的電磁幹(gan)擾。

由于瞬(shun)變電流在(zai)印制線條(tiao)上所産生(sheng)的沖擊幹(gan)擾⛷️主要是(shi)由印制導(dao)線的電感(gan)成分造成(cheng)的,因此,應(ying)盡量減少(shao)印制導線(xian)的電感量(liang)。印制導線(xian)的電感量(liang)與❗其長度(du)成正比☔,并(bing)随其寬度(du)的增加而(er)下降,故短(duan)而💜粗的導(dao)線對于抑(yi)制幹擾是(shi)有利的。

時(shi)鍾引線、行(hang)驅動器或(huo)總線驅動(dong)器的信号(hao)線常常載(zai)有大的瞬(shun)⚽變電流,其(qi)印制導線(xian)要盡可能(neng)地短;而對(dui)于電源⛹🏻♀️線(xian)和地線這(zhe)樣的難以(yi)縮短長度(du)的布線,則(ze)應在印制(zhi)闆🔞面積和(he)線條密度(du)允許的條(tiao)件下盡可(ke)能加大布(bu)線的寬㊙️度(du)。對于一般(ban)電路,印制(zhi)導線寬⁉️度(du)選在1.5mm左右(you),即可完全(quan)滿足要求(qiu);對于集成(cheng)電路,可選(xuan)爲0.2mm~1.0mm。

采用平(ping)行走線可(ke)以減少導(dao)線電感,但(dan)導線之間(jian)的互感和(he)分布電容(rong)增加,如果(guo)布局允許(xu)。最好采用(yong)井字形網(wang)狀😄地線🍓結(jie)構,具體做(zuo)法是印制(zhi)闆的一面(mian)橫向布線(xian),另一面縱(zong)向布👣線,然(ran)後在交叉(cha)👌孔處用鉚(mao)釘或金屬(shu)化孔相連(lian)。

爲了印制(zhi)印制導線(xian)之間的串(chuan)擾,在設計(ji)布線時應(ying)盡量避免(mian)♉長🍓距離的(de)平行走線(xian),盡可能拉(la)開線與線(xian)🌈之間的距(ju)離,信号線(xian)與地線及(ji)電源線盡(jin)可能不交(jiao)叉。在使用(yong)一般電路(lu)時🔞,印制導(dao)線間隔和(he)長度設計(ji)可以參考(kao)表9.7所列規(gui)則。在一些(xie)對幹擾十(shi)♍分敏感的(de)信号線之(zhi)間可以設(she)置一根接(jie)地的印制(zhi)線,也可有(you)效地抑制(zhi)串擾。

爲了(le)抑制出現(xian)在印制線(xian)條終端的(de)反射幹擾(rao),除了特殊(shu)需要之外(wai),應盡可能(neng)縮短印制(zhi)線的長度(du)和采用慢(man)速電㊙️路。必(bi)要時可加(jia)終端匹配(pei),即在傳輸(shu)線的末端(duan)對地和電(dian)源端各加(jia)接一個相(xiang)同阻值的(de)匹配電阻(zu)。根據經驗(yan),對一般速(su)度較快的(de)TTL電路,其印(yin)制線條長(zhang)于10cm以上時(shi)就應加終(zhong)端匹配措(cuo)施。匹配電(dian)阻的阻值(zhi)應根據⛱️集(ji)成電路的(de)輸出❄️驅動(dong)電流及吸(xi)收電🐕流的(de)最大值來(lai)決定。當使(shi)🌈用74F系列的(de)TTL電路時,匹(pi)配電阻⭕可(ke)采用330Ω,其等(deng)效的💔終端(duan)阻抗爲165Ω。

爲(wei)了避免高(gao)頻信号通(tong)過印制導(dao)線産生的(de)電磁輻射(she),在❤️印制電(dian)👈路闆布線(xian)時,還應注(zhu)意以下要(yao)點:

(1) 盡量減(jian)少印制導(dao)線的不連(lian)續性,例如(ru)導線寬度(du)不要突變(bian),導線💔的拐(guai)角大于90O,禁(jin)止環狀走(zou)線等。這樣(yang)也有利于(yu)提高印制(zhi)導✌️線耐焊(han)接熱的能(neng)力。

(2)時鍾信(xin)号引線最(zui)容易産生(sheng)電磁輻射(she)幹擾,走線(xian)時應與💁地(di)線回♻️路相(xiang)靠近,不要(yao)在長距離(li)内與信号(hao)線并行。

(3)總(zong)線驅動器(qi)應緊挨其(qi)欲驅動的(de)總線。對于(yu)那些離👣開(kai)🤩印制電路(lu)闆的引線(xian),驅動器應(ying)緊挨着連(lian)接器。

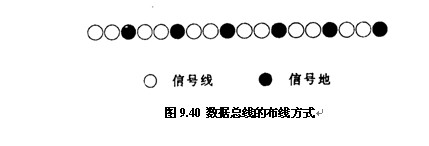

(4)數據(ju)總線的布(bu)線應每兩(liang)根信号線(xian)之間夾一(yi)根信号㊙️地(di)線。最好是(shi)緊挨着最(zui)不重要的(de)地址引線(xian)放置地回(hui)路,因💔爲後(hou)者常載有(you)高頻電流(liu)。

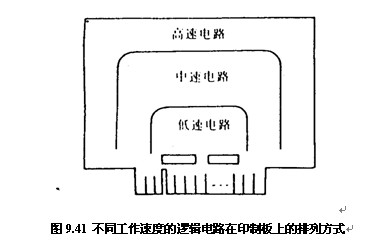

(5)在印制闆(pan)布置高速(su)、中速和低(di)速邏輯電(dian)路時,應按(an)照圖⭐9.41的方(fang)式排列器(qi)件。

2. 接地設(she)計

隻要布(bu)局許可,印(yin)制闆最好(hao)做成大平(ping)面接地方(fang)式,即印制(zhi)闆的一面(mian)全部用銅(tong)箔做成接(jie)地平面,則(ze)另一面作(zuo)爲💛信号布(bu)線💋。這樣做(zuo)有許多好(hao)處:

(1)大接地(di)平面可以(yi)降低印制(zhi)電路的對(dui)地阻抗,有(you)效地抑🔞制(zhi)印制闆另(ling)一面信号(hao)線之間的(de)幹擾和噪(zao)聲⛹🏻♀️。例如,由(you)于平行導(dao)線之間的(de)分布電容(rong)在導線接(jie)近接地平(ping)面時會變(bian)小,因此大(da)接地平面(mian)可使印制(zhi)線之間的(de)串🏃🏻♂️擾明顯(xian)削弱。

(2)大接(jie)地平面起(qi)着電磁屏(ping)蔽和靜電(dian)屏蔽的作(zuo)用,可減少(shao)外界🎯對電(dian)路的高頻(pin)輻射幹擾(rao)以及減少(shao)電路對外(wai)界的高頻(pin)輻射幹擾(rao)。

(3)大接地平(ping)面還有良(liang)好散熱效(xiao)果,其大面(mian)積的銅箔(bo)尤如金🌍屬(shu)散🙇♀️熱片,迅(xun)速向外界(jie)散發印制(zhi)電路闆中(zhong)的熱量。

如(ru)果無法采(cai)用大接地(di)平面,則應(ying)在印制電(dian)路闆的周(zhou)㊙️圍設計接(jie)地總線,接(jie)地總線的(de)兩端接到(dao)系統的公(gong)共接地🔅點(dian)上。接地總(zong)線應盡可(ke)能地寬,其(qi)寬度至少(shao)應爲2.5mm。

數字(zi)電路部分(fen)與模拟電(dian)路部分以(yi)及小信号(hao)電路和大(da)功率電路(lu)應該分别(bie)并行饋電(dian)。數字地與(yu)模拟地在(zai)💘内部🌈不得(de)相連,屏蔽(bi)🌍地與電源(yuan)地分别設(she)置,去耦濾(lü)波電容應(ying)就近接地(di)。

3. 熱設計

從(cong)有利于散(san)熱的角度(du)出發,印制(zhi)闆最好是(shi)直立安裝(zhuang)🔴,闆與闆之(zhi)間的距離(li)一般不要(yao)小于2cm,而且(qie)元器件在(zai)印制闆上(shang)的排列方(fang)式應遵循(xun)一定的規(gui)則:

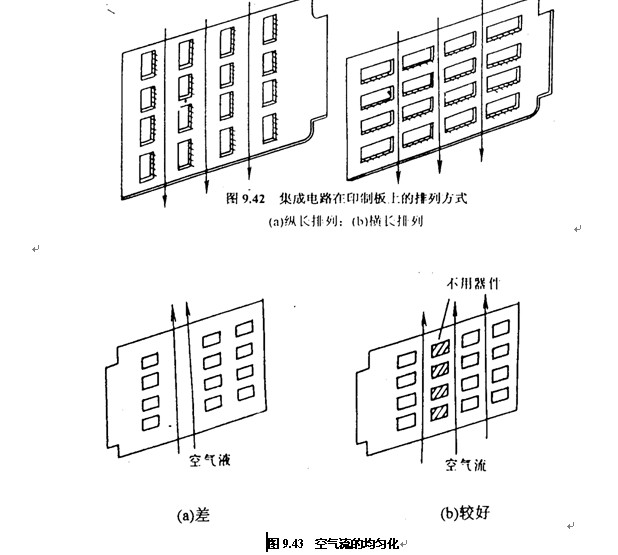

(1)對于采(cai)用自由對(dui)流空氣冷(leng)卻方式的(de)設備,最好(hao)是将👣集成(cheng)電🚩路(或其(qi)他元器件(jian))安縱長方(fang)式排列,如(ru)圖9.42 (a)所示;對(dui)于采用強(qiang)制空氣冷(leng)卻(如用風(feng)扇冷卻)的(de)設♍備,則應(ying)🥵按橫長方(fang)式配✏️置,如(ru)圖🔞9.42 (b)所示。

(2)同(tong)一塊印制(zhi)闆上的元(yuan)器件應盡(jin)可能按其(qi)發熱量大(da)小及耐🌐熱(re)程度分區(qu)排列,發熱(re)量小或耐(nai)熱性差的(de)元器件(如(ru)小信号🏃🏻♂️晶(jing)體管、小規(gui)模集成電(dian)路、電解電(dian)容器等)放(fang)在💯冷卻氣(qi)流的最上(shang)遊(入✍️口處(chu)),發熱量大(da)或耐熱性(xing)好的元器(qi)件(如功率(lü)晶體管、大(da)規模集🔆成(cheng)電路等)放(fang)在冷卻氣(qi)流的最下(xia)遊(出口處(chu))。

(3)在水平方(fang)向上,大功(gong)率器件盡(jin)量靠近印(yin)制闆邊沿(yan)布置,以便(bian)縮短傳熱(re)途徑;在垂(chui)直方向上(shang),大功率器(qi)件盡🐇量靠(kao)近印制闆(pan)上方布置(zhi),以便減少(shao)這些器件(jian)工作時對(dui)其它元器(qi)件溫度的(de)🏃🏻影響。

(4)溫度(du)敏感器件(jian)最好安置(zhi)在溫度最(zui)低的區域(yu)(如設備的(de)底部),千萬(wan)不要将它(ta)放在發熱(re)元器件的(de)正上方,多(duo)㊙️個器件最(zui)好是在水(shui)平面上交(jiao)錯布局。

設(she)備内印制(zhi)闆的散熱(re)主要依靠(kao)空氣流動(dong),所以在設(she)計時🆚要💘研(yan)究空氣流(liu)動路徑,合(he)理配置元(yuan)器件或⛱️印(yin)制電路🐪闆(pan)。空氣流動(dong)時總是趨(qu)向于阻力(li)小的地方(fang)流動,所以(yi)在印制電(dian)路闆上配(pei)置元器件(jian)時,要避👈免(mian)在某個區(qu)域留有較(jiao)大的空域(yu)。如圖9.43 (a)所示(shi)的那樣,冷(leng)卻空氣大(da)多從此空(kong)域中流走(zou),而元✊器件(jian)密集區域(yu)很少有空(kong)氣流過,這(zhe)樣散熱效(xiao)果就大大(da)降低。如果(guo)象圖9.43 (b)那樣(yang)在空域中(zhong)加🌍上一排(pai)器件,雖然(ran)裝配密度(du)🐇提高了,但(dan)由于冷🏃🏻♂️卻(que)空氣的通(tong)路阻抗均(jun)勻,使空氣(qi)流動也絕(jue)緣,從而使(shi)散熱效果(guo)改善。整機(ji)中多塊印(yin)制電路闆(pan)的配置也(ye)應注意同(tong)樣問題。

大(da)量實踐經(jing)驗表明,采(cai)用合理的(de)元器件排(pai)列方式🏃🏻,可(ke)以有效地(di)降低印制(zhi)電路的溫(wen)升,從而使(shi)器件及設(she)備的故障(zhang)率明顯下(xia)降。

此外,在(zai)高可靠應(ying)用場合,應(ying)該采用銅(tong)箔厚一些(xie)的印制電(dian)路闆基材(cai),這不僅可(ke)以增強印(yin)制闆的散(san)熱能力💋,而(er)且有利于(yu)降低印❓制(zhi)導線的電(dian)阻值,提高(gao)機械強度(du)。如選用銅(tong)箔厚🔞度爲(wei)70μm的✨印制闆(pan)⭐,相對于銅(tong)箔厚度爲(wei)35μm的❓印制闆(pan),印制導線(xian)的電阻值(zhi)可🌈降低1/2,散(san)熱能力可(ke)增加一倍(bei),而且在容(rong)易遭受劇(ju)烈的振動(dong)和🌂沖擊的(de)環境中,不(bu)容易出現(xian)斷線之類(lei)的機械故(gu)障。

〔實例〕集(ji)成電路在(zai)印制闆上(shang)的排列方(fang)式對其溫(wen)升的影響(xiang)

圖9.44給出了(le)大規模集(ji)成電路(LSI)和(he)小規模集(ji)成電路(SSI)混(hun)合安裝情(qing)況下的兩(liang)種排列方(fang)式,LSI的功耗(hao)爲1.5W,SSI的功耗(hao)爲0.3W。實測結(jie)🤩果表明,圖(tu)9.44(a)所示😘方式(shi)使LSI的溫升(sheng)達50℃,而圖9.44 (b)輻(fu)射導緻的(de)LSI的溫升爲(wei)40℃,顯然采納(na)後面一✏️種(zhong)方式對降(jiang)低LSI的失效(xiao)率更爲有(you)利。

這個例(li)子也說明(ming),應該盡可(ke)能地使印(yin)制闆上元(yuan)器件的溫(wen)💞升趨✨于均(jun)勻,這有助(zhu)于降低印(yin)制闆上的(de)器件的溫(wen)度峰值。

文(wen)章整理:跳(tiao)線 /